DESIGN WORKFLOW IMPROVEMENTS USING STRUCTURAL MATCHING FOR FAST RE-SYNTHESIS OF ELECTRONIC CIRCUITS

Background

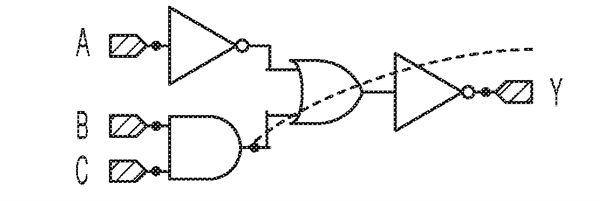

Electronic circuits are growing in complexity every year. Existing workflows that optimize the design and placement of circuit components are laborious and time-consuming though. Incremental design changes that target device optimization can take many hours to render. Streamlined design workflows that are both fast and able to optimize performance are needed to keep pace with these device improvements. A UC Santa Cruz researcher has developed a new technique, SMatch, to shorten design workflow times with minimal QoR impact.

Technology Description

UC Santa Cruz researchers have developed SMatch, a method that uses an incremental FPGA flow to skip placement and routing for matching blocks. This method significantly shortens runtime while maintaining QoR by reducing the overall number of LUTs needed to be placed and routed. SMatch is generally 20x faster than other incremental commercial FPGA flows and is able to deliver many of the changes set by the Anubis benchmark suite in under 30s.

Applications

Advantages

Intellectual Property Information

| Country | Type | Number | Dated | Case |

| United States Of America | Issued Patent | 11,599,700 | 03/07/2023 | 2018-689 |

| United States Of America | Issued Patent | 10,885,246 | 01/05/2021 | 2018-689 |

Related Materials

Contact

- Marc Oettinger

- marc.oettinger@ucsc.edu

- tel: View Phone Number.

Inventors

- Possignolo, Rafael

- Renau, Jose

Other Information

Keywords

Electronic device automation, EDA, Design workflow, Synthesis, Chip design, Structural Netlist, FPGA - Field Programmable Gate Array, Hardware Description Language, Lookup Table