Hi-Frequency, Low Power Nanowire Nanoelectrochemical Field-Effect Transistors

Background

Conventional silicon-based transistors face limitations in continued reduced dimensions in order to make electrons move faster. Meanwhile thermodynamics are dictating the amount of power consumed at the off state - by limiting the subthreshold slope of conventional transistors to be at least 60 mV/dec. Motivated by Moore’s Law, the following technology advances the effort to build low power computer logic and memory elements with even more speed.

Technology Description

Engineers from UC San Diego have developed a novel nanoscale transistor structure that is based on both electrical transport and mechanical deformation in semiconductor nanowire materials and operates under a new mechanism of coupled nanoelectromechanical motion in order to achieve high switching speed as well as low standby power. Compared to traditional MEMS mechanical switches, a suspended field-effect channel does not rely on mechanical contacts with the gate electrode thus offer the advantage of high reliability. More specifically, this technology achieves a sub-threshold slope of zero by leveraging a high-mobility one dimensional nanowire platform.

This device is poised to provide a building block for future computation.

Applications

Low power, high speed transistors (cell phone, computing devices). Disruptive semiconductor technology.

State Of Development

Technology is available for commercial development, patent protection available for US.

Related Materials

- Kim JH., Chen ZC., Kwon S., Xiang J. Three-terminal nanoelectromechanical field effect transistor with abrupt subthreshold slope. Nano Lett. 2014 Mar 12;14(3):1687-91. doi: 10.1021/nl5006355. Epub 2014 Feb 28. PubMed PMID: 24568680. - 02/28/2014

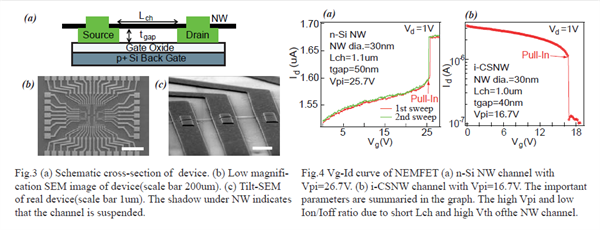

- Kim JH., Zack C.Y. Chen, S. Kwon and J. Xiang. Steep Subthreshold Slope Nanoelectromechanical Field-Effect Transistors with Nanowire Channel and Back Gate Geometry IEEE Explore (Figs. 3 & 4 inset above). - 01/01/2013

Patent Status

| Country | Type | Number | Dated | Case |

| United States Of America | Issued Patent | 9,793,417 | 10/17/2017 | 2013-239 |

Contact

- University of California, San Diego Office of Innovation and Commercialization

- innovation@ucsd.edu

- tel: View Phone Number.